CoWoS,劲敌来了

先进封装,不再是边角料的存在。

知名分析师陆行之表示,棋盘中央如果说先进制程是硅时代的权力中枢,那么先进封装,正在成为下一个技术帝国的边疆要塞。

最近,业内关于先进封装的消息频频,其中又以FOPLP最为突出。

马斯克宣布要跨界入局先进封装,瞄准了FOPLP。旗下 SpaceX涉足将半导体封装,拟于美国得克萨斯州建设自有 FOPLP产能。据悉SpaceX 的 FOPLP 封装基板尺寸为业界最大的 700mm×700mm。日月光投入2亿美元采购设备,在高雄厂建立产线,计划今年年底试产FOPLP。

一、CoWoS的劲敌

先进封装意味着把不同种类的芯片,包括逻辑芯片、存储、射频芯片等,通过封装及堆叠技术整合在一起,以提升芯片性能、缩小尺寸、减少功耗。

现在阶段的先进封装大概可以分为三种:

倒装芯片(Flip chip)。将芯片倒置(有源面朝下)放置在基板上,并通过芯片上的凸点(Bumps)与基板实现电气连接的封装技术。倒装芯片可以算得上半个先进封装,一只脚踩在先进封装的门里,一只脚在门外,算是传统封装与先进封装的过渡产物。

2.5D/3D IC封装。在中介层上垂直堆叠各类芯片,由此缩小接点间距,减少所需空间及功耗,台积电的CoWoS便是属于此类。

扇出型封装。相对于扇入型封装(Fan-In Packaging)来说,扇出型WLP中,RDL可以向外延伸布线,从而提升I/O接点的数量及密度。

因为人工智能的火热,台积电的CoWoS一夜爆红。

当前依赖台积电CoWoS封装的芯片包括英伟达A100、A800、H100、H800、GH200等。

火热的同时,也让台积电的CoWoS封装产能吃紧。目前台积电的CoWoS封装产能大概在每月3.5万片晶圆,约占总收入的7%到9%。预计到2025年末,月产能将提升至每月7万片晶圆,贡献超过10%的收入。到了2026年末,月产能将进一步扩大,提高至超过每月9万片晶圆。根据统计数字,从2022年至2026年,台积电CoWoS封装产能大概以50%的复合年增长率(CAGR)增长。

此前,台积电CEO魏哲家表示,会在今年持续增加CoWoS产能,以满足客户需求。预计2025年,CoWoS的全年营收贡献将从2024年的8%成长至10%。

即使如此,台积电的CoWoS产能仍然无法满足AI 市场的全部需求。除了扩充CoWoS外,半导体厂商也在寻找新的路线。

FOPLP正是能够接棒CoWoS的候选者。

FOPLP可以追溯到FOWLP(扇出型晶圆级封装),这个技术是英飞凌在2004年提出的,后来在2009年开始量产,但是FOWLP只被应用在手机基带芯片上,很快就达到了市场饱和。

FOWLP是基于圆形的晶圆来进行封装,晶圆的形状就像一个圆盘。由于是圆形,在边缘部分会有一些空间难以像方形那样充分利用,相对来说可放置芯片的面积就小一些。

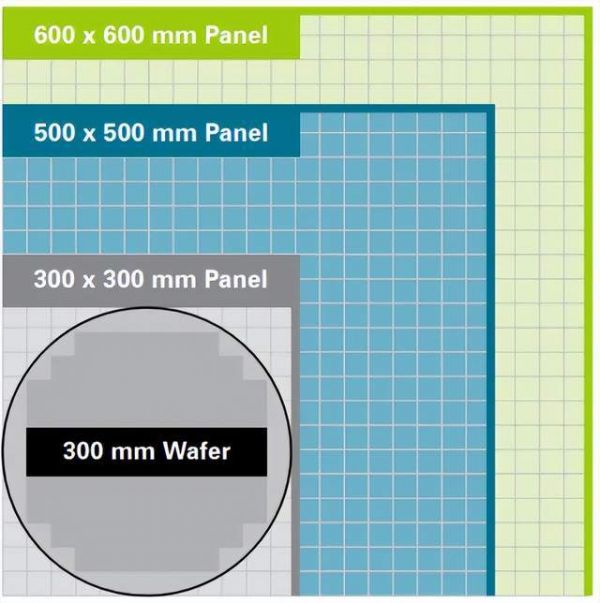

基于FOWLP,业内延伸出了FOPLP(面板级扇出型封装)。两者英文缩写只差在P(Panel)、W(Wafer),面板与晶圆一字之差,影响体现于尺寸与利用率。FOPLP使用的载板,不是8寸/12寸的晶圆,而是方形的大尺寸面板。

这就带来了很多优势。第一是成本低。采用方形的大尺寸面板,那么单片产出的芯片数量就更多,面积利用率更高。以600mm×600mm尺寸的面板为例,面积为12寸wafer carrier的5.1倍,单片产出数量大幅提升。

第二是灵活性高。在FOWLP封装中,光罩的尺寸小,单次曝光面积有上限,需要通过拼接的方式曝光,效率低,良率低,影响产能。而FOPLP封装,单次曝光面积是FOWLP的4倍以上,效率高、良率高,大幅提升了产能。

值得一提的是,FOPLP所使用的玻璃载板材料。

因为FOPLP载板的面积大,在生产和处理的过程中,容易出现翘曲等问题。所以,相比于传统的硅材料,FOPLP的载板材料主要是金属、玻璃或其他高分子聚合物材料。

其中,玻璃在机械、物理、光学等性能上具有明显的优势。当前,玻璃基板已经成为业内关注的焦点。目前布局了玻璃基板的包括台积电、三星、英特尔等大厂。

正因为FOPLP拥有如此出色的表现,未来先进封装中CoWoS不再会是一家独大。

二、谁在入局?

先进封装的成长是非常惊人的。

Yole去年七月报告中指出,受 HPC 和生成式 AI 领域的大势推动,先进封装行业规模有望在六年间实现 12.9% 的复合年增长率(CGAR)。

具体而言,该行业的整体收入将从 2023 年的 392 亿美元增至 2029 年的 811 亿美元(当前约 5897.32 亿元人民币)。

Yole预计FOPLP市场在 2022 年约为 4100 万美元,预计未来五年将呈现 32.5% 的显著复合年增长率,到 2028 年增长到 2.21 亿美元。

目前,三星已经在部署用于先进节点的FOPLP,其用于可穿戴设备的Exynos W920处理器采用了 5nm EUV 技术和 FOPLP。TrendForce报道,谷歌在Tensor G4 芯片中采用了三星的 FOPLP,而 AMD 和 NVIDIA 等公司目前正在与台积电和 OSAT 供应商合作,将 FOPLP 集成到他们的下一代芯片中。

台积电,从小基板入手。

2024年8月,台积电发布公告,计划斥资171.4亿元新台币向群创购买南科厂房及附属设施。台积电CEO魏哲家公开表示,台积电正加速推进FOPLP工艺,目前已经成立了专门的研发团队,并规划建立小规模试产线,力争在2027年量产。

台积电在FOPLP初期选择尺寸较小的 300×300 mm 面板,预计最快 2026 年完成 miniline 小规模产线建设。

据了解,台积电原本倾向515×510 mm 矩形基板,与传统的 12 英寸圆形晶圆相比,这种基板的可用面积可增加三倍。此后又对 600×600 mm、300×300 mm 规格进行了尝试,最终敲定初期先用 300×300 mm练兵,日后再扩展到更大尺寸上。

日月光,布局十年。

日月光投控营运长吴田在今年2月表示,决定在中国台湾高雄厂区投入2亿美元(约新台币66亿元)设立面板级扇出型封装(FOPLP)量产线,预计第二季设备进厂,第三季开始试量产。

日月光十年前即投入FOPLP研发,初期采用300mm×300mm规格,在试作达到不错效果后,尺寸推进至600mm×600mm,并于去年开出设备采购单,相关机台预定第二季及第三季装机,今年底试产,若试产顺利,预定明年送样客户验证后,即可量产出货。

吴田玉认为,若600mm×600mm面板级扇出型封装良率如预期顺利,相信会有更多的客户和产品导入,届时可望成为业界主流规格。随着客户导入面板级扇出型封装,可解决现有12寸晶圆尺寸已不敷使用的问题。

力成科技,小批量出货。

力成是全球封测厂商中第一家建设FOPLP产线的公司,于2016年设立,并在2019年正式导入量产,规格为510*515mm。

目前,力成位于新竹科学园区的全自动FineLine FOPLP封测产线,于2024年6月进入小批量生产阶段。业内人士透露,力成科技已获得联发科电源管理IC封测订单。

力成执行长谢永达在此前表示,经过持续优化,目前510×515毫米的良率大幅超出预期,并获得客户认可。谢永达指出,看好未来在AI世代中,异质封装将采用更多FOPLP解决方案,并预计2026—2027年将导入量产。

长电科技,技术储备。

长电科技是中国大陆最大的半导体封测厂商。

此前,长电科技已明确表示,公司有扇出面板级封装(FOPLP)技术储备。并通过投资者互动平台确认其在高密度扇出型集成封装技术可提供从设计到生产的全流程服务,尤其在算力芯片相关的大尺寸倒装及晶圆级扇出型封装已经积累多年的量产经验,并一直与不同的晶圆厂在最先进制程的硅节点上进行合作。

三、FOPLP,还未放量

按照调研机构集邦调查所说,会采用FOPLP先进封装的产品,主要可分为电源管理IC及射频IC、 和CPU 及GPU、AI GPU 等三类。

目前FOPLP还没有放量。

主要原因除了良率未达理想值以外,标准也尚未定出来。与以200毫米和300毫米标准为主的晶圆级封装不同,不同制造商的面板尺寸差异很大,导致工具和设备设计不一致。通常必须为每种独特的面板尺寸开发定制解决方案。

据Nordson Test & Inspection计算机视觉工程经理John Hoffman表示:“面板面临的最大挑战之一是尺寸缺乏标准化,这决定了系统设计的很大一部分。对于晶圆,我们有 200 毫米和 300 毫米的标准,但面板差异很大。这种差异使系统设计变得复杂,特别是在处理和压平翘曲面板时。”

并且,从当前的企业选择来说,无论是510x515mm、600x600mm为常见规格,目前都还未定。如果无法实现高产线利用率,那么FOPLP 的规模化将成本过高。

相关推荐

CoWoS,劲敌来了

美团小程序终于来了,最大劲敌是百度?

杀疯了的CoWoS

张小龙说的微信短内容「视频号」来了,它能成为抖音、快手的劲敌吗?

台积电CoWoS先进封装产能告急!

传台积电将再建两座CoWoS先进封装厂

蒋尚义:华为是台积电CoWoS首个客户!

台积电回应CoWos封装产能扩充传闻:仍在评估中

台积电计划涨价:3nm涨5%,CoWoS涨20%!

台积电CoWoS扩产计划不变,目标年底产能将达每月7万片

网址: CoWoS,劲敌来了 http://www.xishuta.com/newsview137152.html

推荐科技快讯

- 1问界商标转让释放信号:赛力斯 95792

- 2报告:抖音海外版下载量突破1 25736

- 3人类唯一的出路:变成人工智能 25175

- 4人类唯一的出路: 变成人工智 24611

- 5移动办公如何高效?谷歌研究了 24309

- 6华为 nova14深度评测: 13155

- 7滴滴出行被投诉价格操纵,网约 11888

- 82023年起,银行存取款迎来 10774

- 9五一来了,大数据杀熟又想来, 9794

- 10手机中存在一个监听开关,你关 9519