3nm技术,怎么看

来源:半导体行业观察

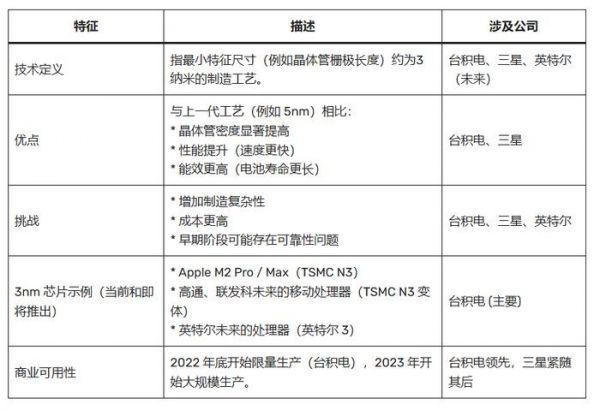

3纳米芯片制造工艺代表了半导体技术的重大进步。这一先进的工艺使得更小、更高效、更强大的微芯片成为可能。三星和台积电已经开始生产3纳米芯片,标志着半导体行业进入了一个新的时代。

3纳米工艺相比前几代在功耗、性能和芯片密度方面都有了显著提升。它使用了先进的制造技术,如全环绕栅极(GAA)晶体管,以实现这些进步。这项技术使得在微小空间内集成数十亿个晶体管成为可能。

芯片制造商们正竞争开发和实施3纳米技术。具备3纳米芯片生产能力的公司在全球半导体市场中占有竞争优势。随着对更快、更高效设备的需求不断增加,3纳米芯片将在未来技术中发挥至关重要的作用。

3纳米制造工艺

3纳米芯片技术:更小、更快、更高效

半导体行业不断发展,制造商们努力制造出更小、更强大且更节能的芯片。3纳米芯片技术站在这一进化的最前沿,代表了半导体制造的一个重要飞跃。

什么是3纳米芯片技术?

“3纳米”指的是芯片上晶体管的尺寸。1纳米是1米的十亿分之一,而在芯片制造中,晶体管更小意味着多个好处:

- 晶体管密度增加:芯片上的晶体管越多,处理能力越强,性能越快。

- 提高能效:更小的晶体管消耗的电能更少,有助于延长设备的电池寿命并减少数据中心的能耗。

- 性能增强:与前代技术相比,3纳米芯片提供了显著的性能提升,实现更快的处理速度和更流畅的多任务处理。

3纳米制造的关键参与者

3纳米芯片的开发和生产是一个复杂且昂贵的过程,只有少数公司拥有必要的专业技术和资源:

- 台积电:作为领先的半导体代工厂,台积电是3纳米芯片的主要制造商之一。

- 三星:另一家主要的半导体公司,三星也在量产3纳米芯片。

- 英特尔:虽然面临一些延迟,但英特尔也在积极推进其3纳米工艺技术。

3纳米芯片的应用

3纳米芯片有望革新多个行业和应用领域:

- 智能手机和平板电脑:未来的移动设备在速度、电池寿命和图形性能上将显著提升。

- 高性能计算:3纳米芯片将为下一代超级计算机和数据中心提供动力,实现更快的科学发现和更高效的数据处理。

- 人工智能:AI应用需要强大的计算能力,3纳米芯片将有助于开发更复杂的AI算法。

- 汽车工业:随着汽车对先进技术的依赖性增加,3纳米芯片将在自动驾驶系统和其他车载功能中发挥关键作用。

挑战和未来

尽管3纳米技术具有许多优势,但它也带来了挑战:

- 制造复杂性:生产3纳米芯片极其复杂,需要最先进的制造设施。

- 成本:3纳米芯片的开发和生产涉及大量投资,可能会影响设备成本。

尽管面临这些挑战,3纳米芯片技术代表了半导体行业的重要里程碑。随着研发的不断推进,我们可以预期未来几年将出现更强大、更高效的芯片,推动各领域的创新。

5纳米芯片技术

虽然3纳米芯片是最新的进步,但5纳米技术在半导体行业仍然具有重要地位。5纳米芯片平衡了性能和效率,广泛应用于各类设备。

5纳米芯片的优势

- 性能提升:5纳米芯片相比旧技术有显著的性能提升。

- 功耗提升:它们消耗更少的电能,有助于延长设备的电池寿命。

- 广泛可用性:5纳米芯片比最新的3纳米芯片更为普及。

5纳米芯片的应用

5纳米芯片为许多当前设备提供动力,包括:

- 智能手机:许多旗舰智能手机采用了5纳米处理器。

- 笔记本电脑:5纳米芯片用于高性能笔记本电脑。

- 游戏主机:最新的游戏主机利用5纳米技术来提升图形和游戏体验。

5纳米与3纳米的比较

5纳米技术仍然是多个应用的强大选项。随着3纳米生产的推进,5纳米芯片将更易获得且更具成本效益,进一步扩展其在各类技术中的应用。

关键要点

- 3纳米芯片制造使得更小、更高效和更强大的微芯片成为可能

- 三星和台积电已开始3纳米芯片的生产,引领行业发展

- 3纳米工艺在功耗、性能和芯片密度方面具有显著提升

半导体制造的演变

近年,半导体制造取得了快速进展,不断突破微型化和性能的极限。这些变化革新了芯片的生产和能力。

从7纳米到3纳米

从7纳米到3纳米的转变标志着半导体技术的重大进步。7纳米芯片于2018年开始量产,提供了改进的性能和能效。2020年推出了5纳米技术,进一步缩小了晶体管尺寸,提高了晶体管密度。

3纳米技术这一最新突破始于2022年。三星率先推出其3纳米全环绕栅极(GAA)工艺,台积电也于当年晚些时候开始高量产。相比前几代,3纳米在功耗、性能和面积(PPA)方面均优于之前的节点。

3nm 相对于 5nm 的关键改进包括:更高的晶体管密度、降低功耗、提高性能。

光刻技术的进步

极紫外 (EUV) 光刻技术对于实现更小的工艺节点至关重要。该技术使用 13.5nm 波长的光来创建极其精细的电路图案。

EUV 优势:更高分辨率、更少的遮罩层数、提高产量。

虽然 EUV 是在 7nm 节点引入的,但其用途已在 5nm 和 3nm 工艺中得到扩展。多重图案化等先进 EUV 技术如今已成为 3nm 生产的关键。

新的沉积和蚀刻方法补充了 EUV 光刻技术。这些工艺可实现精确的材料分层和去除,这对于创建复杂的 3D 晶体管结构至关重要。

扩展及其挑战

随着制造商向 3nm 及更高工艺迈进,他们面临着越来越大的技术和经济挑战。扩展困难包括:量子效应、散热、制造复杂性。

为了解决这些问题,芯片制造商正在探索新的晶体管设计。自 14nm 以来使用的 FinFET 技术已达到极限。GAA 晶体管正在成为下一步,可提供更好的静电控制和可扩展性。

经济挑战也十分严峻。3nm 芯片的设计成本估计为 6.5 亿美元,而 5nm 芯片的设计成本为 4.363 亿美元。这一大幅增长可能会限制 3nm 芯片最初只能应用于大批量、高性能应用。

2nm 和 1nm 等未来节点正在开发中,但需要新材料和制造技术来克服物理限制。

3nm芯片创新与生产

3nm工艺节点代表着半导体制造技术的一次重大飞跃。这项尖端技术有望提高下一代芯片的性能和效率。

台积电的 N3 技术

台积电的 N3 工艺节点标志着芯片制造领域的重大进步。该技术在功耗和性能方面有显著的改进。N3 采用 FinFET 晶体管,借鉴了台积电在之前节点上的经验。

台积电已概述了其 3nm 工艺的几种变体:

N3:初始版本

N3E:增强版,更易访问

N3P、N3S、N3X:适用于不同应用的专用版本

该公司于2022年开始风险生产,并于2022年底实现量产。

三星的 GAA 实现

三星在其 3nm 工艺上采用了不同的方法。该公司使用全栅(GAA) 晶体管,称之为多桥通道场效应晶体管 (MBCFET)。这种设计可以更好地控制电流并减少泄漏。

三星 3nm GAA 的主要特点:

性能优于 FinFET 设计

降低功耗的潜力

更高的设计灵活性

三星将于 2022 年中期开始出货采用其 3GAE(3nm 全环绕栅极早期)工艺的芯片。

进入量产阶段

台积电和三星在 3nm 生产方面都取得了重大进展。台积电于 2022 年 12 月宣布其 N3 工艺批量生产。该公司预计将在 2023 年和 2024 年提高产量。

三星于 2022 年开始出货 3nm 芯片,最初专注于特定应用。该公司计划利用其 3GAP(3nm Gate-All-Around Plus)工艺扩大生产。

3nm生产面临的挑战:

成本高(估计每片晶圆成本高达 20,000 美元)

复杂的设计要求

提高产量的努力

尽管存在这些障碍,两家公司仍在推动 3nm 技术,为更强大、更高效的设备铺平道路。

3nm芯片工艺

重要说明:

“3nm”是一个营销术语:实际技术测量可能因制造商而异。

竞争非常激烈:台积电和三星是目前的主要参与者,而英特尔的目标是在未来几年迎头赶上。

快速发展:预计未来几年 3nm 节点将进一步进步和完善。

3nm半导体制造工艺为芯片技术带来了重大进步。各大公司正在努力克服挑战,将这些尖端芯片推向市场。

3nm半导体制造过程涉及哪些步骤?

3nm 工艺涉及几个关键步骤。这些步骤包括光刻、蚀刻、沉积和封装。极紫外 (EUV) 光刻等先进技术用于在硅片上创建复杂的图案。

整个过程需要专用材料和精确控制。质量控制和测试确保芯片符合性能标准。

目前有哪些公司正在生产3nm半导体?

三星和台积电是 3nm 芯片生产的主要参与者。三星于 2022 年中期开始使用其 Gate-All-Around (GAA) 技术出货 3nm 芯片。

台积电于 2022 年底开始大批量生产 3nm 芯片。其他主要半导体公司也在努力开发自己的 3nm 工艺。

3nm处理器相比前几代在性能和能效方面有哪些提升?

3nm 芯片比以前的节点有显著的提升。它们具有更好的能效、更高的性能和更高的晶体管密度。

台积电声称,与 5nm 技术相比,其 3nm 工艺在相同功率下可将速度提升高达 15%,在相同速度下可将功率降低高达 30%。

3nm 芯片在消费设备中广泛应用的预计时间表是怎样的?

3nm 芯片预计将于 2023 年出现在高端智能手机和平板电脑中。2024 年和 2025 年可能会在消费设备中得到更广泛的应用。

时间表可能因生产能力和设备制造商的需求而异。由于成本较高,初期供应将仅限于高端产品。

就晶体管密度而言,3nm节点尺寸与之前的技术相比如何?

3nm 节点的晶体管密度比之前的节点高得多。它允许在相同的芯片面积内封装更多晶体管。

据报道,台积电 3nm 工艺的逻辑密度比 5nm 工艺高出 1.7 倍,可实现更强大、更高效的芯片设计。

公司在缩小至 3nm 芯片制造规模时面临哪些挑战?

扩展到 3nm 存在重大技术障碍。挑战包括控制量子效应、管理散热以及确保稳定的产量。

这种规模要求的极高精度增加了制造的复杂性和成本。企业必须投入大量资金进行研究和新设备以克服这些障碍。

相关推荐

ASML“掀老底”,称3nm芯片实际为23nm,我们竟被芯片企业营销了

3nm备战进入倒计时

英特尔3nm,加入战局

3nm芯片,被疯抢

苹果豪赌3nm背后

3nm的芯片战争,才刚刚开始

3nm芯片手机,来得有些快!

苹果3nm芯片计划背后

3nm,台积电的一道小坎

最前线丨3nm、5nm制程技术还没捂热,台积电又要开始研发2nm的芯片了

网址: 3nm技术,怎么看 http://www.xishuta.com/newsview128110.html

推荐科技快讯

- 1问界商标转让释放信号:赛力斯 95792

- 2报告:抖音海外版下载量突破1 25736

- 3人类唯一的出路:变成人工智能 25175

- 4人类唯一的出路: 变成人工智 24611

- 5移动办公如何高效?谷歌研究了 24309

- 6华为 nova14深度评测: 13155

- 7滴滴出行被投诉价格操纵,网约 11888

- 82023年起,银行存取款迎来 10774

- 9五一来了,大数据杀熟又想来, 9794

- 10手机中存在一个监听开关,你关 9519