JEDEC公布新一代内存模块标准,以推动HPC和AI应用

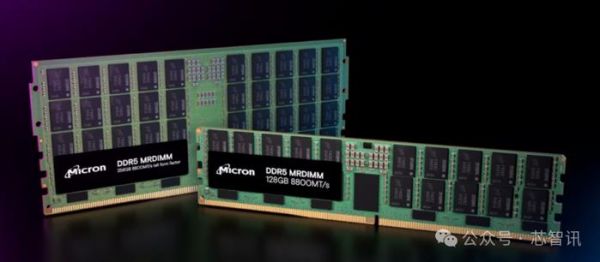

7月23日,JEDEC 固态技术协会宣布了即将推出的 DDR5 多路复用列双列直插式内存模块 (MRDIMM) 和 LPDDR6 的下一代压缩连接内存模块 (CAMM) 标准的关键细节,旨在为下一代高性能计算和 AI 应用提供动力。

面向 LPDDR6 的全新 MRDIMM 和 CAMM 将以无与伦比的带宽和内存容量彻底改变行业。

DDR5 MRDIMM 提供创新、高效的新模块设计,可提高数据传输速率和整体系统性能。多路复用允许在单个通道上组合和传输多个数据信号,无需额外的物理连接即可有效增加带宽,并提供无缝带宽升级,使应用能够超过 DDR5 RDIMM 数据速率。其他计划的功能包括:

与 RDIMM 的平台兼容性,可实现灵活的最终用户带宽配置;

使用标准 DDR5 DIMM 组件,包括 DRAM、DIMM 外形尺寸和引脚分配、SPD、PMIC 和 TS,便于采用;

使用 RCD/DB 逻辑处理功能实现高效的 I/O 扩展;

利用现有的 LRDIMM 生态系统进行设计和测试基础设施;

支持多代扩展至 DDR5-EOL。

JEDEC MRDIMM 标准旨在提供高达原生 DRAM 两倍的峰值带宽,使应用程序能够超越当前数据速率并达到新的性能水平。它保持与 JEDEC RDIMM 相同的容量、可靠性、可用性、可维护性 (RAS) 功能。该委员会的目标是将带宽增加一倍,达到 12.8 Gbps,并提高引脚速度。MRDIMM 设想支持两个以上的等级,并设计为利用标准 DDR5 DIMM 组件,确保与传统 RDIMM 系统兼容。

目前正在计划采用高 MRDIMM 外形尺寸,以提供更高的带宽和容量,而无需更改 DRAM 封装。这种创新、更高的外形尺寸将使 DIMM 上安装的 DRAM 单芯片封装数量增加一倍,而无需 3DS 封装。

作为 JEDEC JESD318 CAMM2 内存模块标准的后续,JC-45 正在为 LPDDR6 开发下一代 CAMM 模块,目标是最大速度大于 14.4 GT/s。按计划,该模块还将提供 24 位子通道、48 位通道和连接器阵列。

这两个项目都在JEDEC的JC-45 DRAM模块委员会中开发中,之后可能会发生变化,包括JEDEC董事会可能对部分内容的不批准。

编辑:芯智讯-浪客剑

发布于:天津

相关推荐

JEDEC公布新一代内存模块标准,以推动HPC和AI应用

Rambus发布DDR5服务器PMIC:支持数据中心内存模块

美光推出 LPCAMM2 内存模块,速率可达 9600MT/s

目标 17600 MT/s,AMD 与 JEDEC 合作开发 DDR5 MRDIMM 内存标准

SK 海力士:CAMM 内存将登陆台式机

DRAM技术,迎来新进展

狂奔的AI,撞上“内存墙”

内存的故事:Rambus之战

美光,押错宝?

澜起科技:新型AI芯片LPU采用大容量、高性价比、可扩展的DRAM模组

网址: JEDEC公布新一代内存模块标准,以推动HPC和AI应用 http://www.xishuta.com/newsview122726.html

推荐科技快讯

- 1问界商标转让释放信号:赛力斯 95792

- 2报告:抖音海外版下载量突破1 25736

- 3人类唯一的出路:变成人工智能 25175

- 4人类唯一的出路: 变成人工智 24611

- 5移动办公如何高效?谷歌研究了 24309

- 6华为 nova14深度评测: 13155

- 7滴滴出行被投诉价格操纵,网约 11888

- 82023年起,银行存取款迎来 10774

- 9五一来了,大数据杀熟又想来, 9794

- 10手机中存在一个监听开关,你关 9519