三星的先进工艺蓝图

编者按:本文来自微信公众号“半导体行业观察”(ID:icbank),作者 David Schor,36氪经授权发布。

本文由公众号半导体行业观察(ID:icbank)翻译自「wikichip」,作者:DavidSchor。

三星在7nm的缓慢进步与EUV的准备状态紧密相关。在过去的一年里,我们看到产量慢慢地提高到可以接受的水平。当前部署的NXE:3400B系统的工作功率为250W或更高。这一点,以及诸如正常运行时间等其他几项改进,意味着EUV现在已经为大批量生产做好了准备。

随着三星终于通过Exynos9825将其7nm工艺推向市场,现在该关注下一代工艺节点了。

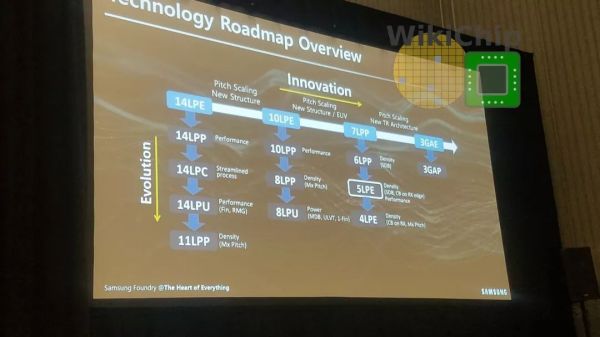

路线图

该路线图与我们去年报告的路线图非常相似,但是有许多有趣的变化。从总体上讲,三星将坚持他们几年前概述的战略——生产4个主要节点,并通过各种PPA增强功能衍生出规模较小且增量较大的后续节点。为此,三星目前正处于7LPP阶段。路线图中的第一个修改是插入一个新的6nm节点。三星今年早些时候在台积电宣布其6nm节点的同一周插入了6nm节点。三星6LPP只是引入了SDB,从而使密度提高了1.18倍。另一个变化是删除了4LPP节点,只在路线图上保留了4LPE,稍后我们将对此进行更详细的讨论。最后,三星将3GAAE和3GAAP更名为3GAE和3GAP。

三星的路线图是过去三家领先公司中风险最低的路线图。每个进化节点都是高度渐进的,通常只引入一个变化。这使得他们可以通过剥离一些先前引入的可扩展的助推器,并在后续节点上添加它们来降低新节点的风险。这样做的缺点是三星的主要节点相当分散,在PPA方面,它们落后于台积电。

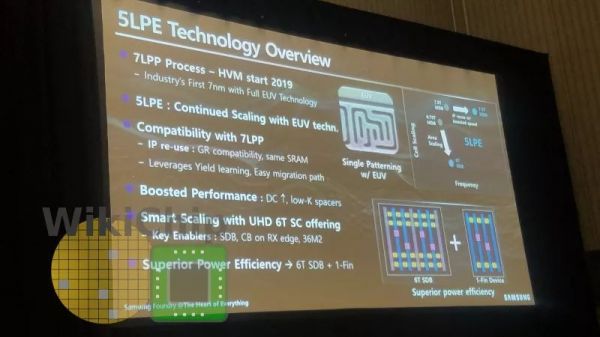

5LPE

从总体上看,5LPE节点实际上是三星7nm工艺的延伸,并计划在借鉴7LPP的基础上,作为第二代EUV工艺。为此,5LPE使用相同的7LPP晶体管、SRAM并提供GR兼容性。

然而,5LPE确实引入了一些新的增强功能。最大的改进是新的6TUHD库,它带有SDB、36nmM2,以及有源区图案(RXN/RXP)边缘上的CB。对于超低功耗/常开晶体管,三星还增加了单鳍片器件。

PPA

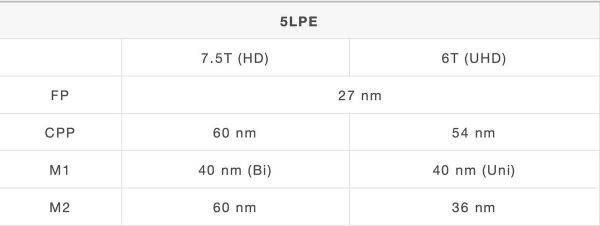

5LPE与7LPP相比具有许多优势,具体取决于所选择的迁移路径。通过改进晶体管,三星声称在使用5LPE7.5T库时,其7LPP工艺的性能提高了11%。或者说,迁移到6T库将使密度提高0.7倍。

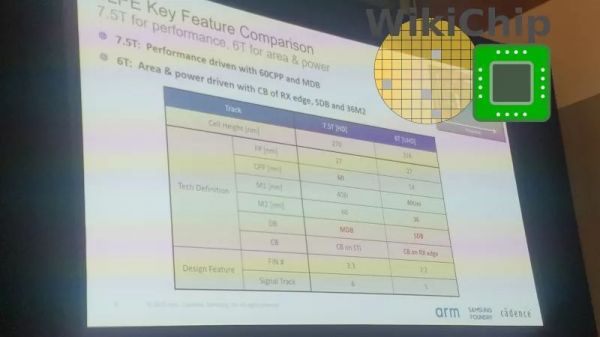

这两个库之间的差异很小,并且具有与7LPP相同的晶体管——相同的FP,相同的PP,但外形略有改善。HD库为3p+3n,具有60nm的多晶间距(polypitch)和MDB。UHD是具有SDB的2p+2n,并使用了54nm的更紧凑的多晶间距(polypitch)。

了解三星标准单元库演进的更好方法是通过性能/有源扩散线(activediffusionline)/单元比较。目前的趋势是在7HP上使用10条扩散线,在7HD或5HD上使用9条扩散线,在5UHD上使用8条扩散线。与三星的10nm相比,它的7LPP每个鳍片有更高的驱动电流,因此,从每个单元相同数量的扩散线开始即可提供更高的性能。

随着收缩,每个单元的PPA会更好。8nm和7nm的高密度电池都去掉了一个鳍片,在与之前的节点性能类似的情况下,提供了更好的面积。新的5nmUHD单元通过去除另一个鳍片进一步延续了这一趋势,当与略微增强的晶体管结合使用时,可提供略微更好的功率区域改善(但不是性能),至少在理论上和总体上是如此。

新的超高密度(UHD)6T库取代了以前的具有9条扩散线的7LPPHD库。新的UHD库删除了另一条扩散线,从而产生了216nm的单元高度。这里的新功能是在有源RXN/RXP边缘上引入CB。

三星还增加了单鳍低泄漏器件,据报道,这种器件可降低多达20%的功耗。

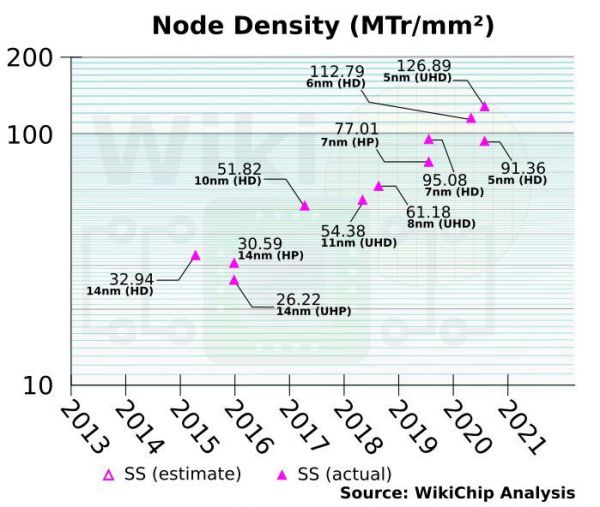

根据我们的估计,三星5nm节点UHD单元的密度已达到接近130MTr/mm²,这是三星第一个密度超过英特尔10nm和台积电7nm的节点。值得补充的是,明年年初,台积电将升级其N5节点,该节点的密度比三星提供的任何产品都要高。鉴于这一时机,我们还预计台积电将在三星5LPE之前推出N5。

三星节点密度(WikiChip分析)

4LPE

三星的最后一个FinFET节点将是4LPE节点。4LPE与5LPE相似,但是将M1的间距从40nm缩小到28nm,M3的间距从36nm缩小到32nm。我们还听说三星计划将鳍片间距减小到25nm,但我们无法正式确认。根据我们目前掌握的为数不多的数字,我们估计4LPE具有137mtr/mm²的单元级晶体管密度。预计到2021年左右,与台积电N5和英特尔7nm节点相比,这将是密度最低的工艺。

相关推荐

三星的先进工艺蓝图

半导体主流先进制程工艺梳理

华为7亿美元紧急下单台积电?先进制程工艺不容乐观

三星获得高通5G芯片代工订单,采用5纳米工艺

三星半导体的未来在何方?

三星半导体死磕台积电:将放弃4纳米工艺直接过渡到3纳米

台积电披露3nm工艺更多细节,明年试产

三星被传收购NXP和格芯,打的什么算盘?

芯片制程之战:三星台积电挺进3nm,英特尔们呢?

实现2nm工艺突破,台积电为何能给“摩尔定律”续命?

网址: 三星的先进工艺蓝图 http://www.xishuta.com/newsview11885.html

推荐科技快讯

- 1问界商标转让释放信号:赛力斯 95792

- 2报告:抖音海外版下载量突破1 25736

- 3人类唯一的出路:变成人工智能 25175

- 4人类唯一的出路: 变成人工智 24611

- 5移动办公如何高效?谷歌研究了 24309

- 6华为 nova14深度评测: 13155

- 7滴滴出行被投诉价格操纵,网约 11888

- 82023年起,银行存取款迎来 10774

- 9五一来了,大数据杀熟又想来, 9794

- 10手机中存在一个监听开关,你关 9519