OPPO加入自研芯片战团,近1800家自主芯片设计公司背后藏大坑

编者按:本文来自微信公众号“魔铁的世界”(ID:jiangpeiyu0916),作者:魔铁,36氪经授权发布。

近日,手机行业爆出一条新闻:OPPO启动代号“马里亚纳计划”,正式加入自研SoC芯片战团。实际上,手机厂商自研SoC芯片并不新鲜。从2014年起,先后有小米、中兴旗下中星微电子宣布自研芯片,加上早已入局的苹果、华为、三星和LG,手机厂商自研芯片掀起一片热潮。

然而,潮水退去后,真正能持续输出产品的仅有苹果、华为和三星,其它厂商基本上都成了炮灰。

正因为如此,OPPO的入局被认为是跳坑,带有一丝悲壮的味道。但如果我们放宽视野,就会发现自研芯片如果仅仅是烧钱的话,其实不算事,还有比烧钱更难的事横在整个国内芯片设计公司面前,使得整个自主手机SoC芯片设计到现在还没有解决卡脖子问题。

01 烧钱只是小坑

手机是快消电子产品,一年一换代,相应地SoC芯片也需要一年一更新,而随着芯片制程工艺的提高,整个研发投入(包括设计、流片)也呈越来越高的趋势。华为fellow艾伟透露,麒麟980采用7nm制程工艺,研发投入超过3亿美元,耗时36个月。

据估计,随着5nm制程工艺量产,芯片的研发投入也将跳涨到50亿元人民币。

这种高强度的“烧钱”节奏,已经促使华为和高通这样有上亿出货量保证的厂商发展出一种“手术刀”策略:通过阉割旗舰版内核(删减或增加IP核的缓存容量、基带速度、内存带宽、内核数量,提高或降低内核频率),搭配出不同档次的中低端SoC芯片。

网友关于OPPO自研芯片的漫画,暗指芯片烧钱。

高通的中端5G芯片骁龙765G的CPU内核和骁龙730的相同,都是基于ARM的A76内核,但频率相差200MHz,GPU、NPU和ISP等均是小改款。

“刀法”娴熟的直接好处是节省了IP授权费(一核多用),降低了芯片设计成本(少养一支设计团队),缩短了芯片的开发周期(高中低档次的芯片项目可以同时进行),最终降低了设计风险。

这一商业策略尽管被不少用户吐槽,但它确实让大厂构筑起一道阻挡潜在竞争对手的高墙:市场的后来者因为没有吃透内核的集成设计技术,缺乏迭代的资源,想阉割也找不到动“刀”的对象,难以降低设计风险和设计成本。

高昂的设计成本、风险和缺乏迭代资源,是OPPO等市场后来者需要面对的一个坑。但和后面的坑比起来,烧钱只是一个小坑。

02 SoC设计难度的大坑:华为花了10年跨过

SoC芯片设计表面上看是内核集成设计,目前市场上有公开的各种IP核售卖,只要买到IP核就可以设计SoC芯片,看起来门槛很低,其实不然。

和基本属于硬件设计范畴的传统芯片设计不同,SoC芯片设计既要面对复杂的逻辑,还要考虑软件,特别是可以改变芯片功能的外部软件的设计,例如操作系统(OS)。换句话说,SoC芯片设计需要软硬件协同。

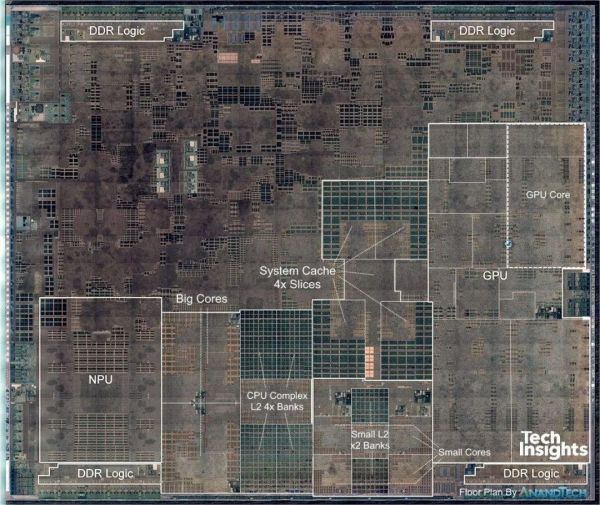

SoC芯片设计除考虑传统的连线延迟问题外,还必须考虑电源噪声、衬底噪声耦合等信号完整性问题。现在手机SoC芯片内集成的晶体管动辄数十亿个,集成度大幅提升的同时,单个芯片中的连线长度也随之大幅提升,连线总长达到几十千米的比比皆是。

苹果A12芯片内部复杂的布局。

稍有物理学知识的人都知道,频率与波长成反比,当芯片的内部工作时钟达到几千MHz的时候,相应的波长只有几米,当工作时钟达到GHz级别时(目前手机旗舰芯片的CPU内核工作时钟接近3GHz),相应的波长会缩短到几十厘米。

根据电磁场相关理论,当连线的长度达到波长的某个倍数时,连线将成为向外界发射电磁波的天线,同样这些连线也将成为接收电磁波的天线,加上芯片内部连线错综密布,结果是SoC芯片内部信号的干扰将成为一个严重问题,影响内核性能稳定并增大功耗,导致SoC芯片“低分低能”。

简单说就是信号的完整性是SoC芯片设计的一个大门槛,解决不好往往会影响内核性能发挥。华为海思花了10年时间,在2014年推出成熟可用的麒麟920之后,才算真正迈过设计门槛,进入正常迭代的轨道。小米的澎湃芯片在推出第一代后,第二代即一直跳票,至今仍在坑里奋斗,足见SoC芯片设计之难。

但即使跳过了SoC芯片设计难度的坑,还有一个更大的坑在等着所有国产SoC芯片设计厂商。

03 自主芯片热闹背后更大的坑

根据ICCAD公布的数据,2019年中国大陆芯片设计公司已达到1780家,相比2018年增加了82家,这已经是自2012年以来,国内芯片设计企业连续保持8年增长。

从数据上看,自主芯片设计相当热闹,就指令集来说,已经涵盖CISC和RISC两大生态系统,按技术来源划分,自研芯片又覆盖了五大阵营:

MIPS阵营,代表龙芯(2009年购买了MIPS指令集永久授权);

ARM阵营,代表有飞腾、海思麒麟、展讯;

IBM Power阵营,代表有宏芯;

X86阵营,代表兆芯(VIA授权)、海光(AMD授权架构);

DEC公司(2001年已被惠普康柏合并),代表申威处理器(购买Alpha架构)。

但细究之下,热闹的背后其实隐忧不少,最大的隐忧是缺少自主设计的IP核。

宏芯、兆芯和海光依靠购买微架构,IP核自主研发能力最弱,相当于IBM、VIA和AMD在中国的马甲产品。

ARM阵营同样是谨慎乐观。ARM的商业策略是只开放微架构(可花钱购买IP核,并可以修改),但指令集是封闭的,指令集的扩展由ARM说了算。这会带来什么问题呢?即使像华为这样设计能力较强的公司,尽管已经获得ARMv8指令集永久授权,但无法自行扩展指令集,还需要继续购买ARMv9指令集,否则即使能自行开发IP核,但由于指令集的禁锢,CPU的性能提升路径依然会被锁死。

ARM借助指令集和IP核授权,建立起庞大的商业生态帝国。

换句话说,ARM通过独揽指令集大权,使飞腾、海思麒麟和展讯等要么购买其IP核,要么围绕其指令集开发CPU核(苹果的A系列芯片就是如此),总之一切尽在ARM掌握之中:如果飞腾、海思麒麟和展讯只购买IP核,等于脖子直接被拽在别人手里;如果飞腾、海思麒麟和展讯自行开发IP核,但由于缺少扩展指令集的权利,迫于软件兼容的压力,还是必须跟着ARM的指挥棒跑,等于脖子间接被拽在别人手里。

04 产业链真正闭环

前一段时间,有权威专家认为国内芯片设计能力进步巨大,完全有能力设计自己的芯片,不怕卡脖子。这话要掰开分析,所谓的设计能力进步巨大,主要是指SoC芯片的集成设计,代表是华为和展锐,但移动IP核包括CPU和GPU(图像处理芯片),目前国内还是一片空白。

没有强大的移动IP核设计打底,自主SoC芯片设计将成为空中楼阁,所以自研芯片的重中之重是IP核的自研,尤其是GPU和CPU核的自主设计。

实际上真正不怕卡脖子的是在电脑CPU领域,代表是龙芯和申威。由于申威购买了已经消失的美国DEC公司的Alpha架构,等于在无主之地上开发IP核并迭代,而且CPU主要用在超算上,所以不怕进清单。

龙芯则是因为在2009年购买了MIPS架构的永久授权,获得IP核后可以自行扩展指令集,所以发展无拘无束,但代价是需要自行培养从操作系统、应用软件到市场用户的庞大生态系统,等于一家干了英特尔、微软、几千家应用软件开发商的活,所以前路漫长。

仅凭龙芯和申威单枪匹马,还难以将我国的IP核自主设计提升到无惧外来压力的水准,未来的出路还是在开源指令集上,在财富效应引领下,吸引大量的芯片设计创业公司入局,自主设计出大量的CPU、GPU、内存控制器、NPU、ISP等IP核,为自主SoC芯片设计提供充足的“原材料”,从而使自主芯片设计在IP核设计、SoC芯片设计、芯片制造、封装、测试等整个产业链条完成真正的闭环,此时谁也卡不了中国芯的脖子。

要达到这一目标,不仅要舍得烧钱,更要舍得花时间沉淀,培养产业链。

相关推荐

OPPO加入自研芯片战团,近1800家自主芯片设计公司背后藏大坑

国产手机公司加码自研芯片,坚持就不会被“卡脖子”

5G芯片争夺战:高通掉队华为赶超,米OV自研路艰难困苦

苹果自研芯片 U1,未来有望用在更多设备上

依图科技发布自研云端芯片questcore™

36氪独家 | 蔚来计划自研芯片,李斌正积极推动

雷军大扫货:一口气投了三家芯片公司

潮科技|「聚芯微电子」发布背照式、高分辨率ToF传感器芯片

谷歌首颗自研SoC芯片成功流片:5nm制程8核设计,或明年落地Pixel 5手机

特斯拉自动驾驶靠自研芯片,国产智能汽车怎么办?

网址: OPPO加入自研芯片战团,近1800家自主芯片设计公司背后藏大坑 http://www.xishuta.com/newsview18060.html

推荐科技快讯

- 1问界商标转让释放信号:赛力斯 95792

- 2报告:抖音海外版下载量突破1 25736

- 3人类唯一的出路:变成人工智能 25175

- 4人类唯一的出路: 变成人工智 24611

- 5移动办公如何高效?谷歌研究了 24309

- 6华为 nova14深度评测: 13155

- 7滴滴出行被投诉价格操纵,网约 11888

- 82023年起,银行存取款迎来 10774

- 9五一来了,大数据杀熟又想来, 9794

- 10手机中存在一个监听开关,你关 9519