为什么28nm光刻机哪怕上“多曝”,也做不到7nm?(中)

接上一篇内容《为什么28nm光刻机哪怕上“多曝”,也做不到7nm?(上)》,前两个问题:28nm光刻机是什么,如何定义?和决定光刻机的最小精度有哪些因素,什么叫套刻精度?相关的内容已经都讲过了,今天开始聊第三个问题:晶体管的实际参数的定义和物理意义,以及相关的知识。

第四个问题多曝工艺/SAQP四曝工艺的详细图解得下次再讲,主要是我虽然理解,但是我得找个会搞PS的人帮我做图,我自己尝试手绘了一下实在是太丑了……还得找专业的人来干这活,有在杭州的PS大神,记得喊我一下,我请你喝茅台咖啡,帮我弄一下图。

等我这几篇科普长文都敲完之后,我到时候出一篇完整的精简版,把所有知识点和内容整理一遍,做到一气呵成,更加方便普通人学习半导体行业知识。

以下是正文:

三、晶体管的实际参数及定义

上一篇已经举例了28nm的实际gate length从40nm-31nm有好几个版本,相信大家都已经理解了。

也知道从28nm开始,所谓的工艺节点和实际晶体管的gate length的大小已经不是一一对应,而是等效关系。

接下来我们进入更深的层次探讨。晶体管大小的实际参数一共有多少个,工程师们是如何定义它们的?

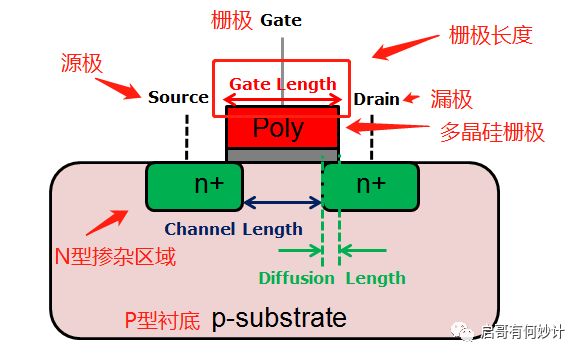

我们再把这张图拿出来复习。

之所以会用gate length栅极长度,实际上因为这个距离是source到drain的距离,也就是晶体管源极到漏极之间的距离。

这个长度距离是集成电路所谓的集成度的标志,也是集成电路工艺技术水准的标志,因此它有时候也被称为关键尺寸或者特征尺寸——CD(critical dimension的缩写)。

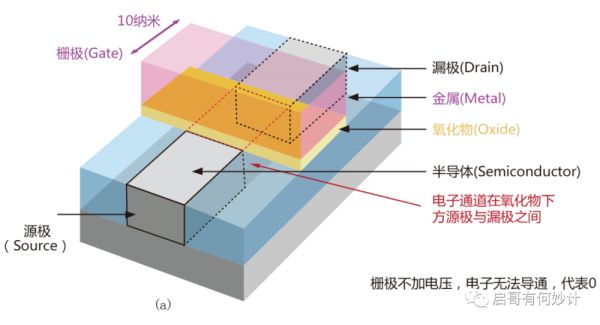

这里补充一点MOSFET晶体管的工作原理。

栅极上加电压后,两个N型掺杂区域之间会形成导通区域,导通情况下晶体管就能被代表为1,不加电压后关断就可以表示成0,有了0和1就组成了计算机计算原理的本质——二进制原理。

这个二进制原理就是微积分大神莱布尼茨提出来的。

这么多年来,摩尔定律一直在前进,晶体管在不断微缩,也就是说栅极距离在不断被拉近,并且以每一代0.7x的速度在减小,两代就是0.7*0.7=0.49,刚好就是一半0.5左右。

因此大家看到的英特尔的工艺节点演进就变成从90*0.7到65nm,65*0.7到45nm,45nm*0.7到32nm,32*0.7到22nm,22*0.7到14nm,14*0.7到10nm。10nm之后英特尔也改了命名规则,变成intel 7(原10ESF/10+++),intel 4(原7nm),intel 3(原7nm+/7nm++),intel 20A(原5nm)。目前到这个20A为止,A也是长度单位,1nm=10A,相当于1埃等于0.1nm,一个原子的大小。

这是英特尔的工艺路线,但是因为英特尔主要做CPU,另外一家专注于先进工艺的台积电,是干逻辑代工的,工艺略有不同,所以中间台积电有跳代的情况出现。

实际上,台积电的工艺节点变化变成90,65/55,40,28,20,16,10,N7,N5,N3。55nm工艺比较特殊,主要是给eFLASH用的,到现在为止还在用,也有部分CIS工艺用这个,还有蓝牙。

台积电体系里,20-10-5nm,是一组研发开发的,而14-7-3是另外一组研发开发的,这就是台积电为了保持工艺领先,搞了两组人,分别在两个技术路线上竞赛。因为当时10nm那组难产,没过多久7nm那组就起来了,两者相差一年都不到,客户没怎么用上10nm,就纷纷直接转去用7nm工艺了。实际上,台积电的10nm就没啥客户来流过片。

所以就有了摩尔定律:每隔18个月,同面积下晶体管数量翻倍,但是价格不变。

数量翻倍就是因为晶体管的面积只有原来的0.5x大小。

但是追溯历史我们可以发现,除了gate length之外,衡量晶体管大小还有另外一个重要指标,叫half pitch,也就是半间距。

前文提到过,过去通常用gate length栅极距离这个来定义,但是到现在变成half pitch半间距来定义。

原因是这样来的:

纵观历史,在远古的6英寸年代,也就500nm线宽时代,当时工艺节点,半间距,以及栅极长度都一样,你用啥都一样,甚至行业习惯是用half pitch来定义工艺节点名称。

但是从350nm时代开始,也就是8英寸工艺起步点,大约是将近30年前,标志性事件就是当年IBM砸了10亿美金的东菲什基尔8英寸线成功投产。1995年前后,情况有变化了。

在此之间,栅长gate length和半间距half pitch都是同步缩小,同时晶体管密度按比例增加,所以当时的工艺节点不管是定义gate length还是half pitch都一样, 但是在此之后,两者不再同步。

实际上衡量晶体管大小,其实有两个指标,栅长gate length和半间距half pitch。在350nm到28nm之间,业内定下来,一直通用栅长gate length来指代工艺节点,直到14nm开始因为情况又有了巨大的变化,又回到用半间距half pitch来标称工艺节点。

而且那会儿开始就搞等效工艺的概念了。

原因就是上文提到的,取决于芯片内部最大密度晶体管密度数,从沟道长度变成了最小金属层间距,因此又回到half pitch来定义芯片了。

为什么会这样?关于half pitch的实际物理意义,我咨询了镇群大佬河哥,河哥给了一个很复杂的回复,我整理一下大致是这样的:

因为在光刻胶工艺上,也有正负胶之分(正负胶,像石碑的阴刻或者阳刻),一个pitch,就是一次光照的明暗变化,半个就是亮或暗。按照正胶或者负胶的不同,都可以代表最小线宽或者最小特征尺寸,所以会叫半间距。

在实际晶体管中,沟道宽度(channel length )和MOS管体积密切相关,沟道越小密度越高,又因为金属层连接沟道,基本每根金属线宽度等于沟道宽度,所以最小金属间距等于每个MOS管间距,也就是CD(critical dimension),特征尺寸。

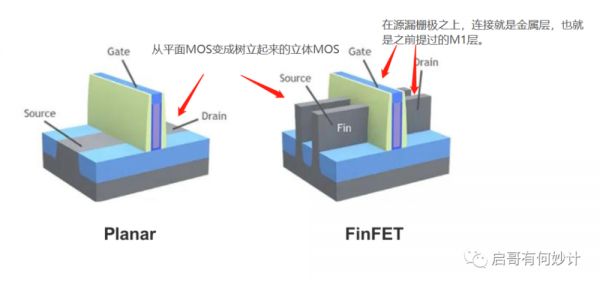

到了22nm以下的FinFET时代,因为结构变化金属线宽度不再等同于沟道宽度,但是MOS管从平面变成每个竖起来的,但还是需要3根金属线分别连接源极,漏极,栅极来传递信号和供能,所以密度最高间距最小数值的,反而变成第一次互联的金属层了。金属层密度一定程度上代表了晶体管密度,所以在FinFET结构下最小间距就变成金属层,而光刻机在金属层能最小做到多少pitch,就基本代表了整个芯片的密度。

我给大家总结一下:在平面MOS时代,也就28nm以上工艺,half pitch代表channel length,也就是沟道距离;但是在FinFET时代,也就是22nm以下工艺,half pitch的实际物理意义,是变成第一层最小金属之间间距的一半。

两者是有区别的。

这段历史也确实够混乱的,我也是整了半天才明白。

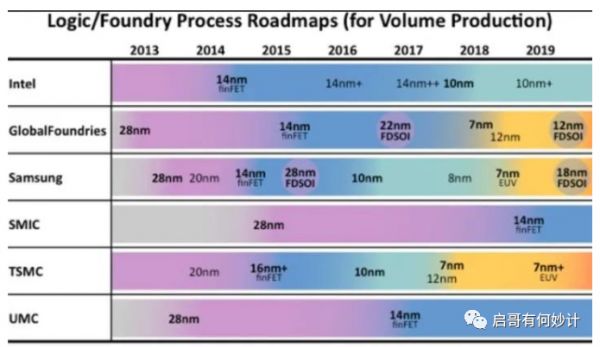

在22nm时代之后,各种制程变得眼花缭乱,都变成玩文字游戏。除了英特尔之外的厂家,比如三星,台积电,都挖空心思在等效工艺节点命名上做文章,从而在命名上完成对英特尔的“各种超越”。

最终出现台积电的N7=英特尔10nm这种神奇的情况。

甚至还有格罗方德当年22nm的FD-SOI=14nm这种更加神奇的理解。

2013-2019年,逻辑代工厂的技术路线图

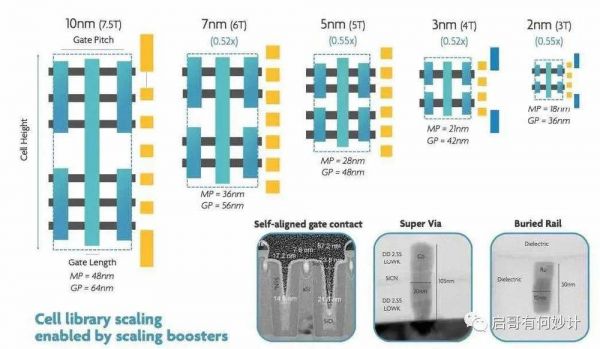

这种混乱的情况持续了很长一段时间,惹得英特尔的工艺框架和集成总监Mark同志发飙,质疑其他家所谓的N7/7nm工艺,到底有没有自家10nm工艺这样栅极距离是54nm这么小的线宽。

当时他还发表了一篇名为《让我们清理半导体工艺命名的混乱》的文章。在这篇文章中,Mark直指业界在半导体工艺命名上的混乱状态,并给出了一个衡量半导体工艺水平的公式,目标直指当时三星和台积电的老六行为。

我也是从那时候开始,终于彻底明白过来,今天才有机会给大家完整科普,等效工艺这个信息含量巨大,且复杂、最容易误解、最有争议的集成电路工艺概念。

我相信认真看完我长文的读者,现在也明白过来,所谓的“几nm”,只是代表某种特定尺寸技术的商业名称,并不指代实际的栅极长度或者半间距长度。

上图也可以看出,尽管英特尔在命名上没有胜出,但是实际各项指标都是优于竞争对手的。

插入一个FinFET结构示意图帮助大家理解:

回到用金属层最小间距的14nm年代后,我们发现用栅极距离和最小金属互联距离,两个尺寸可以围起来变成一个方框,用来衡量一个晶体管的面积。当然,实际上这不是完全绝对,但是从某种意义上来讲,方框面积越小,晶体管密度就越高。

未完待续。

本文来自微信公众号:启哥有何妙计(ID:qgyhmj),作者:陈启

相关推荐

为什么28nm光刻机哪怕上“多曝”,也做不到7nm?

为什么28nm光刻机哪怕上“多曝”,也做不到7nm?(中)

为什么“28nm光刻机”多重曝光也做不到7nm?

为什么是28nm?

“赌”输了?中芯国际停止生产28nm芯片,美媒:美日荷计划得逞了

台积电高雄厂28nm暂停,改建5~7nm以下制程

传台积电高雄28nm厂暂停,将改建5~7nm以下制程

中芯国际方向对了!28nm、40nm产能利用率达100%,中国客户抢单

制造的天花板:聊聊台积电和中芯国际的未来抉择

中兴7nm芯片商用之际,中芯国际7nm制程“取得突破”

网址: 为什么28nm光刻机哪怕上“多曝”,也做不到7nm?(中) http://www.xishuta.com/newsview90187.html

推荐科技快讯

- 1问界商标转让释放信号:赛力斯 95792

- 2报告:抖音海外版下载量突破1 25736

- 3人类唯一的出路:变成人工智能 25175

- 4人类唯一的出路: 变成人工智 24611

- 5移动办公如何高效?谷歌研究了 24309

- 6华为 nova14深度评测: 13155

- 7滴滴出行被投诉价格操纵,网约 11888

- 82023年起,银行存取款迎来 10774

- 9五一来了,大数据杀熟又想来, 9794

- 10手机中存在一个监听开关,你关 9519